- 您现在的位置:买卖IC网 > Sheet目录364 > SST49LF080A-33-4C-WHE-T (Microchip Technology)IC FLASH SER LPC 8MBIT 32TSOP

�� �

�

�

�8� Mbit� LPC� Flash�

�A� Microchip� Technology� Company�

�SST49LF080A�

�Data� Sheet�

�LPC� Mode�

�Device� Operation�

�The� LPC� mode� uses� a� 5-signal� communication� interface,� a� 4-bit� address/data� bus,� LAD[3:0],� and� a�

�control� line,� LFRAME#,� to� control� operations� of� the� SST49LF080A.� Cycle� type� operations� such� as�

�Memory� Read� and� Memory� Write� are� defined� in� Intel� Low� Pin� Count� Interface� Specification,� Revision�

�1.0.� JEDEC� Standard� SDP� (Software� Data� Protection)� Program� and� Erase� commands� sequences� are�

�incorporated� into� the� standard� LPC� memory� cycles.� See� Figures� 7� through� 12� for� command�

�sequences.�

�LPC� signals� are� transmitted� via� the� 4-bit� Address/Data� bus� (LAD[3:0]),� and� follow� a� particular�

�sequence,� depending� on� whether� they� are� Read� or� Write� operations.� LPC� memory� Read� and� Write�

�cycle� is� defined� in� Tables� 5� and� 6.�

�Both� LPC� Read� and� Write� operations� start� in� a� similar� way� as� shown� in� Figures� 5� and� 6.� The� host�

�(which� is� the� term� used� here� to� describe� the� device� driving� the� memory)� asserts� LFRAME#� for� two� or�

�more� clocks� and� drives� a� start� value� on� the� LAD[3:0]� bus.�

�At� the� beginning� of� an� operation,� the� host� may� hold� the� LFRAME#� active� for� several� clock� cycles,� and�

�even� change� the� Start� value.� The� LAD[3:0]� bus� is� latched� every� rising� edge� of� the� clock.� On� the� cycle�

�in� which� LFRAME#� goes� inactive,� the� last� latched� value� is� taken� as� the� Start� value.� CE#� must� be�

�asserted� one� cycle� before� the� start� cycle� to� select� the� SST49LF080A� for� Read� and� Write� operations.�

�Once� the� SST49LF080A� identifies� the� operation� as� valid� (a� start� value� of� all� zeros),� it� next� expects� a�

�nibble� that� indicates� whether� this� is� a� memory� Read� or� Write� cycle.� Once� this� is� received,� the� device� is�

�now� ready� for� the� Address� cycles.� The� LPC� protocol� supports� a� 32-bit� address� phase.� The�

�SST49LF080A� encodes� ID� and� register� space� access� in� the� address� field.� See� Table� 3� for� address� bits�

�definition.�

�For� Write� operation� the� Data� cycle� will� follow� the� Address� cycle,� and� for� Read� operation� TAR� and�

�SYNC� cycles� occur� between� the� Address� and� Data� cycles.� At� the� end� of� every� operation,� the� control� of�

�the� bus� must� be� returned� to� the� host� by� a� 2-clock� TAR� cycle.�

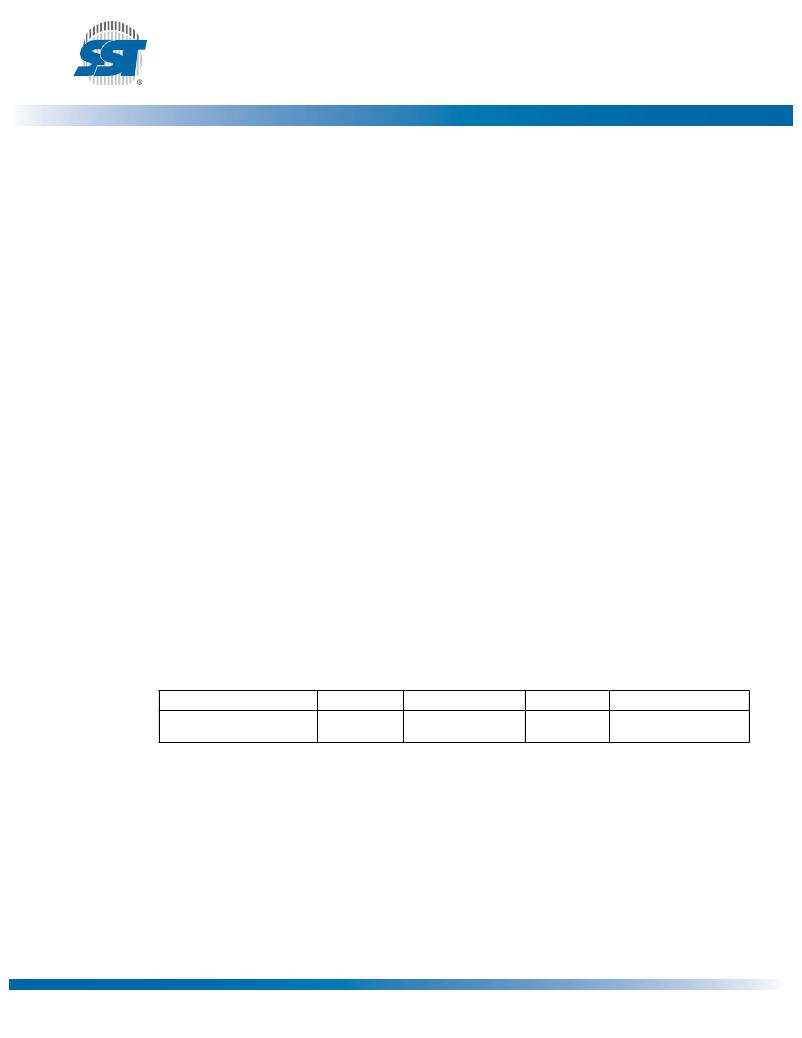

�Table� 3:� Address� bits� definition�

�A� 31� :� A� 251�

�1111� 111b� or� 0000� 000b�

�A� 24� :A� 23�

�ID[3:2]� 2�

�A� 22�

�1� =� Memory� Access�

�A� 21� :� A� 20�

�ID[1:0]� 2�

�A� 19� :A� 0�

�Device� Memory� address�

�0� =� Register� access�

�T3.1� 25026�

�1.� The� top� 32MByte� address� range� FFFF� FFFFH� to� FE00� 0000H� and� the� bottom� 128� KByte� memory� access� address�

�000F� FFFFH� to� 000E� 0000H� are� decoded.�

�2.� See� Table� 7� for� multiple� device� selection� configuration�

�?2011� Silicon� Storage� Technology,� Inc.�

�8�

�DS25086A�

�11/11�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SST49LF160C-33-4C-NHE

IC FLASH SER LPC 16MBIT 32PLCC

ST40

DIAC 35-45V BILATERAL TRIG DO214

STRIKER

SURGE SUPPRESSR 120V 7OUT 6'CORD

SUPER-7

SURGE SUPPRESSOR 7 OUT 7' CORD

SUPER6TEL12

SURGE SUPPR 7OUT 12'CORD W/RJ11

SUPER6TEL

SURGE SUPPRESSOR 7OUT W/TEL

SUPER7COAX

SURGE SUPPRESSOR 7 OUT W/COAX

SUPER7TEL15

SURGE SUPPR 7OUT 15'CORD W/RJ11

相关代理商/技术参数

SST49LF160C

制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:16 Mbit LPC Flash

SST49LF160C334CNHE

制造商:Microchip Technology Inc 功能描述:

SST49LF160C-33-4C-NHE

功能描述:闪存 16M (2Mx8) 33MHz 3.0-3.6V Commercial RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel

SST49LF160C-33-4C-NHE_

制造商:Microchip Technology Inc 功能描述:

SST4H-D

功能描述:电缆束带 Cable Tie, 2-Piece, 14.8"L (376mm), Ligh RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4H-D0

功能描述:电缆束带 14.8" BLK CABLE TIE RELEAS WEATHER RES RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4H-D30

功能描述:电缆束带 Cable Tie, 2-Piece, 14.8"L (376mm), Ligh RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4HH-D

制造商:Panduit Corp 功能描述: